## M58WR016KU M58WR016KL M58WR032KU M58WR032KL

## 16- or 32-Mbit (×16, Mux I/O, Multiple Bank, Burst) 1.8 V supply Flash memories

Data Brief

## Features

- Supply voltage

- $V_{DD}$  = 1.7 V to 2 V for Program, Erase and Read

- $V_{DDQ} = 1.7$  V to 2 V for I/O buffers

- V<sub>PP</sub> = 9 V for fast Program

- Multiplexed address/data

- Synchronous / Asynchronous Read

- Synchronous Burst Read mode: 86 MHz

- Random access: 60 ns, 70 ns

- Synchronous Burst Read Suspend

- Programming time

- 10 µs by word typical for Factory Program

- Double/Quadruple Word Program option

- Enhanced Factory Program options

- Memory blocks

- Multiple Bank memory array: 4 Mbit Banks

- Parameter Blocks (top or bottom location)

- Dual operations

- Program Erase in one Bank while Read in others

- No delay between Read and Write operations

- Block locking

- All blocks locked at Power up

- Any combination of blocks can be locked

- WP for Block Lock-Down

- Security

- 128 bit user programmable OTP cells

- 64 bit unique device number

- Common Flash Interface (CFI)

- 100 000 program/erase cycles per block

- Electronic signature

- Manufacturer Code: 20h

- Top device code,

M58WR016KU: 8823h

M58WR032KU: 8828h

- Bottom device code, M58WR016KL: 8824h M58WR032KL: 8829h

- ECOPACK® packages available

January 2007

1/10

## 1 Description

The M58WR016KU/L and M58WR032KU/L are 16-Mbit (1 Mbit  $\times$ 16) and 32- Mbit (2 Mbit  $\times$ 16) non-volatile Flash memories, respectively. In the rest of the document, they will be referred to as M58WRxxxKU/L unless otherwise specified.

The M58WRxxxKU/L may be erased electrically at block level and programmed in-system on a word-by-word basis using a 1.7 V to 2 V V<sub>DD</sub> supply for the circuitry and a 1.7 V to 2 V V<sub>DDQ</sub> supply for the Input/Output pins. An optional 9 V V<sub>PP</sub> power supply is provided to speed up customer programming.

The first sixteen address lines are multiplexed with the Data Input/Output signals on the multiplexed address/data bus ADQ0-ADQ15. The remaining address lines, A16-Amax, are the Most Significant Bit addresses.

The device features an asymmetrical block architecture:

- the M58WR016KU/L have an array of 39 blocks, and are divided into 4 Mbit banks. There are 3 banks each containing 8 main blocks of 32 KWords, and one parameter bank containing 8 parameter blocks of 4 KWords and 7 main blocks of 32 KWords.

- the M58WR032KU/L have an array of 71 blocks, and are divided into 4 Mbit banks. There are 7 banks each containing 8 main blocks of 32 KWords, and one parameter bank containing 8 parameter blocks of 4 KWords and 7 main blocks of 32 KWords

The Multiple Bank Architecture allows Dual Operations, while programming or erasing in one bank, Read operations are possible in other banks. Only one bank at a time is allowed to be in Program or Erase mode. It is possible to perform burst reads that cross bank boundaries. The Parameter Blocks are located at the top of the memory address space for the M58WR016KU and M58WR032KU, and at the bottom for the M58WR016KL and M58WR032KL.

Each block can be erased separately. Erase can be suspended, in order to perform program in any other block, and then resumed. Program can be suspended to read data in any other block and then resumed. Each block can be programmed and erased over 100 000 cycles using the supply voltage  $V_{DD}$ . There are two Enhanced Factory programming commands available to speed up programming.

Program and Erase commands are written to the Command Interface of the memory. An internal Program/Erase Controller takes care of the timings necessary for program and erase operations. The end of a program or erase operation can be detected and any error conditions identified in the Status Register. The command set required to control the memory is consistent with JEDEC standards.

The device supports synchronous burst read and asynchronous read from all blocks of the memory array; at power-up the device is configured for asynchronous read. In synchronous burst mode, data is output on each clock cycle at frequencies of up to 86 MHz. The synchronous burst read operation can be suspended and resumed.

The device features an Automatic Standby mode. When the bus is inactive during Asynchronous Read operations, the device automatically switches to the Automatic Standby mode. In this condition the power consumption is reduced to the standby value  $I_{DD4}$  and the outputs are still driven.

The M58WRxxxKU/L features an instant, individual block locking scheme that allows any block to be locked or unlocked with no latency, enabling instant code and data protection. All blocks have three levels of protection. They can be locked and locked-down individually preventing any accidental programming or erasure. There is an additional hardware protection against program and erase. When  $V_{PP} \leq V_{PPLK}$  all blocks are protected against program or erase. All blocks are locked at Power-Up.

The device includes a Protection Register to increase the protection of a system's design. The Protection Register is divided into two segments: a 64 bit segment containing a unique device number written by ST, and a 128 bit segment One-Time-Programmable (OTP) by the user. The user programmable segment can be permanently protected.

The memory is available in a VFBGA44 7.5  $\times$  5 mm, 10  $\times$  4 active ball array, 0.5 mm pitch package. It is supplied with all the bits erased (set to '1').

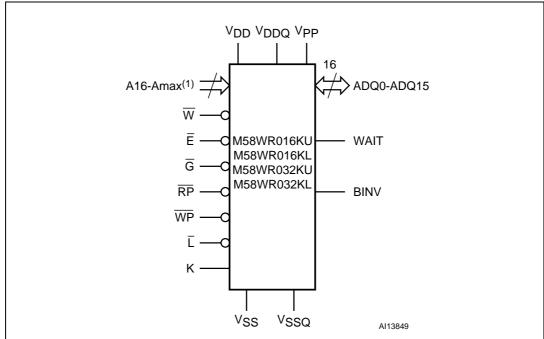

Figure 1. Logic diagram

1. Amax is equal to A19 in the M58WR016KU/L and, to A20 in the M58WR032KU/L.

| Signal name             | Function                                             | Direction |  |

|-------------------------|------------------------------------------------------|-----------|--|

| A16-Amax <sup>(1)</sup> | Address inputs                                       | Inputs    |  |

| ADQ0-ADQ15              | Data Input/Outputs or Address Inputs, Command Inputs | I/O       |  |

| Ē                       | Chip Enable                                          | Input     |  |

| G                       | Output Enable                                        | Input     |  |

| W                       | Write Enable                                         | Input     |  |

| RP                      | Reset/Power-down                                     | Input     |  |

| WP                      | Write Protect                                        | Input     |  |

| К                       | Clock                                                | Input     |  |

| T                       | Latch Enable                                         | Input     |  |

| WAIT                    | Wait                                                 | Output    |  |

| BINV                    | Bus Invert                                           | Input     |  |

| V <sub>DD</sub>         | Supply voltage                                       |           |  |

| V <sub>DDQ</sub>        | Supply voltage for input/output buffers              |           |  |

| V <sub>PP</sub>         | Optional supply voltage for fast Program & Erase     |           |  |

| V <sub>SS</sub>         | Ground                                               |           |  |

| V <sub>SSQ</sub>        | Ground input/output supply                           |           |  |

| NC                      | Not connected internally                             |           |  |

### Table 1.Signal names

1. Amax is equal to A19 in the M58WR016KU/L and, to A20 in the M58WR032KU/L.

| Figure |     |   | nnections       | <u>(())</u>               | <u></u>         | <u>p</u> | -, |    | Al13848                                            |

|--------|-----|---|-----------------|---------------------------|-----------------|----------|----|----|----------------------------------------------------|

| 14     | NON |   |                 |                           |                 |          |    | NC |                                                    |

| 13     |     |   |                 |                           |                 |          |    |    |                                                    |

| 12     |     |   | NC              | V <sub>SSQ</sub>          | (IO)            | ADQ0     |    |    |                                                    |

| 1      |     |   | A17             | (ш)                       | ADQ8            | ADQ1     |    |    |                                                    |

| 10     |     |   | A19             | A18                       | ADQ9            | VDDQ     |    |    |                                                    |

| 6      |     |   | dq <sup>V</sup> | <u>₩</u>                  | ADQ2            | ADQ10    |    |    | KU/L.                                              |

| ø      |     |   | .  ≥            | ₽<br>L                    | ADQ3            | ADQ11    |    |    | 158WR016                                           |

| 7      |     |   | VDD             | BINV                      | ADQ12           | ADQ4     |    |    | Not Connected internally (NC) in the M58WR016KU/L. |

| 9      |     |   | ×               |                           | ADQ13           | ADQ5     |    |    | l internally (                                     |

| Q      |     |   | <sup>V</sup> SS | A20/<br>NC <sup>(1)</sup> | ADQ6            | VSSQ,    |    |    | t Connected                                        |

| 4      |     |   | NC              | A16                       | ADQ7            | ADQ14    |    |    |                                                    |

| ю      |     |   | WAIT            | VDDQ                      | <sup>V</sup> SS | ADQ15    |    |    | 58WR032KI                                          |

| 2      |     |   |                 |                           |                 |          |    |    | 20 in the Mŧ                                       |

| ~      | NC  |   |                 |                           |                 |          |    | NC | Note1: Ball D5 is A20 in the M58WR032KU/L, it is   |

|        | <   | ۵ | U               | ۵                         | ш               | Ŀ        | U  | т  | Note1:                                             |

Figure 2. VFBGA44 connections (top view through package)

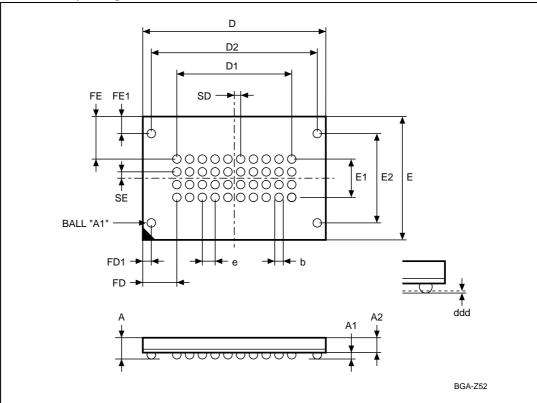

## 2 Package mechanical

In order to meet environmental requirements, ST offers the M58WRxxxKU/L in ECOPACK® packages. These packages have a Lead-free second-level interconnect. The category of Second-Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97.

The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: *www.st.com*.

Figure 3. VFBGA44 7.5 × 5 mm, 10 × 4 ball array, 0.50 mm pitch, bottom view package outline

1. Drawing is not to scale.

| Symbol |       | millimeters |       | inches |        |        |  |

|--------|-------|-------------|-------|--------|--------|--------|--|

|        | Тур   | Min         | Max   | Тур    | Min    | Max    |  |

| А      |       |             | 1.000 |        |        | 0.0394 |  |

| A1     |       | 0.150       |       |        | 0.0059 |        |  |

| A2     | 0.660 |             |       | 0.0260 |        |        |  |

| b      | 0.300 | 0.250       | 0.350 | 0.0118 | 0.0098 | 0.0138 |  |

| D      | 7.500 | 7.400       | 7.600 | 0.2953 | 0.2913 | 0.2992 |  |

| D1     | 4.500 |             |       | 0.1772 |        |        |  |

| D2     | 6.500 |             |       | 0.2559 |        |        |  |

| ddd    |       |             | 0.080 |        |        | 0.0031 |  |

| Е      | 5.000 | 4.900       | 5.100 | 0.1969 | 0.1929 | 0.2008 |  |

| E1     | 1.500 |             |       | 0.0591 |        |        |  |

| E2     | 3.500 |             |       | 0.1378 |        |        |  |

| е      | 0.500 | _           | _     | 0.0197 | _      | _      |  |

| FD     | 1.500 |             |       | 0.0591 |        |        |  |

| FD1    | 0.500 |             |       | 0.0197 |        |        |  |

| FE     | 1.750 |             |       | 0.0689 |        |        |  |

| FE1    | 0.750 |             |       | 0.0295 |        |        |  |

| SD     | 0.250 |             |       | 0.0098 |        |        |  |

| SE     | 0.250 |             |       | 0.0098 |        |        |  |

# Table 2.VFBGA44 7.5 × 5 mm, 10 × 4 ball array, 0.50mm pitch, package<br/>mechanical data

## 3 Part numbering

| Table 3.      Ordering information scheme              |       |         |             |

|--------------------------------------------------------|-------|---------|-------------|

| Example:                                               | M58 W | R 032 K | U 70 ZA 6 E |

|                                                        |       |         |             |

| Device Type                                            |       |         |             |

| M58                                                    |       |         |             |

| Architecture                                           |       |         |             |

| W = Multiple Bank, Burst Mode                          |       |         |             |

| Operating Voltage                                      |       |         |             |

| $R = V_{DD} = V_{DDQ} = 1.7 \text{ V to } 2 \text{ V}$ |       |         |             |

|                                                        |       |         |             |

| Density                                                |       |         |             |

| 016 = 16 Mbit (×16)                                    |       |         |             |

| 032 = 32 Mbit (×16)                                    |       |         |             |

|                                                        |       |         |             |

| Technology                                             |       |         |             |

| K = 65 nm technology                                   |       |         |             |

| 5                                                      |       |         |             |

| Parameter Location                                     |       |         |             |

| U = Top Boot, Mux I/O                                  |       |         |             |

| L = Bottom Boot, Mux I/O                               |       |         |             |

| Speed                                                  |       |         |             |

| 60 = 60 ns                                             |       |         |             |

| 70 = 70 ns                                             |       |         |             |

|                                                        |       |         |             |

| Package                                                |       |         |             |

| ZA = VFBGA44 7.5 x 5 mm, 0.50 mm pitch                 |       |         |             |

| Temperature Range                                      |       |         |             |

| 6 = -40 to 85 °C                                       |       |         |             |

|                                                        |       |         |             |

| Option                                                 |       |         |             |

|                                                        |       |         |             |

E = ECOPACK® Package, Standard Packing

U = ECOPACK® Package, Tape & Reel Packing, 16mm

Devices are shipped from the factory with the memory content bits erased to '1'.

For a list of available options (Speed, Package, etc.), Daisy chain ordering information, or for further information on any aspect of this device, please contact the ST Sales Office nearest to you.

## 4 Revision history

### Table 4.Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 30-Jan-2007 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com